# THE SIMULATION OF ELECTRICAL I-V CHARACTERISTICS OF THE BIPOLAR JUNCTION TRANSISTOR (BJT) SEMICONDUCTOR BY USING PISCES IIB.9009

LIEW KANG SOO

DISSERTATION SUBMITTED AS PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF BACHELOR OF SCIENCE WITH HONOURS

> PHYSICS WITH ELECTRONICS PROGRAMME SCHOOL OF SCIENCE AND TECHNOLOGY UNIVERSITI MALAYSIA SABAH

> > MAY 2008

PUMS99:1

# UNIVERSITI MALAYSIA SABAH

| BORANG PEN                                                                                                       | GESAHAN STATUS TESIS@                                                                                                                                                                                                                |

|------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UDUL THE SIMULATION OF ELECT                                                                                     | RICAL 1-6 CHARACTERISTICS OF THE                                                                                                                                                                                                     |

| BIPOLAR SUNCTION TRANSISTOR                                                                                      | (BTT) SEMICONDUCTOR BT USING PISCES BB. 400                                                                                                                                                                                          |

| IAZAH: 3-Se CHong)                                                                                               |                                                                                                                                                                                                                                      |

| AYA LIEW KANG SOO                                                                                                | SESI PENGAJIAN: 1007/2008                                                                                                                                                                                                            |

| (HURUF BESAR                                                                                                     | ) SEST PENGAJIAN: 100 ( 100 C                                                                                                                                                                                                        |

| eengaku membenarkan tesis (LPSM/Sarjana/<br>Ialaysia Sabah dengan syarat-syarat kegunaa                          | Doktor Falsafah) ini disimpan di Perpustakaan Universiti<br>n seperti berikut:-                                                                                                                                                      |

| <ol> <li>Tesis adalah hakmilik Universiti Ma</li> <li>Perpustakaan Universiti Malaysia Sa<br/>sahaja.</li> </ol> | ilaysia Sabah.<br>abah dibenarkan membuat salinan untuk tujuan pengajian                                                                                                                                                             |

|                                                                                                                  | salinan tesis ini sebagai bahan pertukaran antara institutsi                                                                                                                                                                         |

| SULIT                                                                                                            | (Mengandungi maklumat yang berdarjah keselamatan atau<br>Kepentingan Malaysia seperti yang termaktub di dalam<br>AKTA RAHSIA RASMI 1972)                                                                                             |

|                                                                                                                  | (Mengandungi maklumat TERHAD yang telah ditentukan oleh organisasi/badan di mana penyelidikan dijalankan)                                                                                                                            |

| TIDAK TERHAD                                                                                                     | Disahkan Oleh                                                                                                                                                                                                                        |

| KAB1.                                                                                                            |                                                                                                                                                                                                                                      |

| (TANDATANGAN PENULIS)                                                                                            | (TANDATANGAN PUSTAKAWAN)                                                                                                                                                                                                             |

| lamat Tetap: 94, Persiaran Desa                                                                                  |                                                                                                                                                                                                                                      |

| ngkalan 5, Taman Desor<br>ngkalan Indah, 71500 Zahar, Pemal                                                      | c . Nama Penyelia                                                                                                                                                                                                                    |

| arikh: 12/5/2008                                                                                                 | Tarikh:                                                                                                                                                                                                                              |

| /organisasi berkenaan dengan<br>dikelaskan sebagai SULIT dan<br>@Tesis dimaksudkan sebagai te                    | HAD, sila lampirkan surat daripada pihak berkuasa<br>menyatakan sekali sebab dan tempoh tesis ini perlu<br>TERHAD.<br>sis bagi Ijazah Doktor Falsafah dan Sarjana secara<br>pengajian secara kerja kursus dan Laporan Projek Sarjana |

## DECLARATION

I hereby declare that this dissertation contains my original research work. Sources of finding reviewed here in have been duly acknowledged.

15 May 2008

LIEW KANG SOO

HS2005-2447

**CERTIFIED BY**

Signature

2.

1. SUPERVISOR

(PROF. MADYA DR. ABDULLAH CHIK)

(DR. HAIDER F. ABDUL AMIR)

Beletch Chil

108

3. EXAMINER 2 (MR. SAAFIE SALLEH)

EXAMINER 1

4. DEAN

-

(SUPT/KS, PROF. MADYA DR. SHARIFF A. K. OMANG, ADK)

SHON MARCANZ

## ACKNOWLEDGEMENT

First and foremost, I would like to express my gratitude to my supervisor, Prof. Madya Dr. Abdullah Chik for his supervision along this final year project. Without his constant guidance, I would not have finished this dissertation.

Besides my supervisor, I would like to thank my course-mate, Thong De Sheng, for her helps in solving the problems that I faced along this final year project. Thanks are extended to my housemates in Sabah who had kept encouraging me. Heartiest appreciation to my housemates, for their never ending support throughout my study.

Last, but not least. I thank my family, especially my parents for giving me unconditional support and encouragement. I would like to thank my brother too. Thank you so much!

LIEW KANG SOO HS2005-2447

#### ABSTRACT

PISCES-IIB device simulator is used to study the characteristics silicon (Si) base bipolar junction transistor device. The difference of concentration, depth and width parameters of BJT will affect the electrical I-V characteristics. A bipolar junction transistor (BJT) is a type of transistor. It is a three-terminal device constructed of doped semiconductor material and may be used in amplifying or switching applications. Si is used in this study because Si is the existence of silicon dioxide, one of the best insulators. Silicon dioxide can easily be incorporated onto silicon circuits. POSTMINI is used to read the mesh files from the simulation programs PISCES-IIB and allows the user to examine or plot quantities stored in the mesh file. The most important part in BJT is output characteristics common emitter current-voltage curve. For common emitter arrangement, they have three regions, such as saturation region, active region and cut-off region. The collector curves in this study are not flat but increase slightly with collector voltage. For the given transistor model, the curves would be flat because the collector current-source's current output is not affected by the voltage across it. But actual transistors are better modeled by including a resistance (r<sub>o</sub>) from collector to emitter. It typically has a large value and can usually be disregarded. The collector curves slope downward toward the left and intersect the Vcc axis at VA Ideal Ic should have been flat because minority slope remains intact, A second feature of the collector curves is that they voltage saturate below 0.1 V.

## ABSTRAK

Pensimulasi peranti PISCES-IIB digunakan untul mengkaji ciri-ciri silikon transistor dwikutub. Perbazaaz ketumpatan, kelebaran dan ketebalan lapisan Bipolar Junction Transistor (BJT) akan memberi kesan terhadap mengkaji ciri-ciri elektrik IV. Transistor dwikutub ialah sejenis transistor. Ia merupakan cantuman tiga bahagian semikonduktor dan boleh digunakan sebagai aplikasi amplifier dan suis. Si digunakan dalam kajian kerana Si kewujudan silikon dioksida. Silikon dioksida adalah salah satu penebat yang sangat baik. Silikon dioksida senang mengabungkan dalam litar silikon. POSTMINI adalah digunakan untuk membaca fail mesh daripada program simulasi PISCES-IIB dan memberikan pengguna memeriksa kuantiti plot yang disimpan dalan fail mesh. Bahagian yang paling penting dalam BJT ialah cirri keluaran tatarajah pemancar sepunya. Bagi susunan pemancar sepunya, ia terdapat tiga kawasan, iaitu kawasan ketepuan, kawasan operasi dan kawasan pemotongan. Tatarajah pemungut dalam kajian tidaj datar tetapi pertambahan sedikit dengan voltan pemungut. Ciri keluaran tatarajah contoh transistor yang diberi adalah datar kerana arus pemungut tidak terjejas oleh voltan pemancar sepunya. Akan tetapi transistor sebenar adalah contoh yang baik bagi termasuk rintangan (ro) daripada pemungut kepada pemancar. Ia biasanya menpunyai nilai yang besar dan biasanys boleh tidak mempedulikan. Kecerunan tatarajah pemungut dipanjangkan ke kiri dan bersilang paksi Vce di VA. Ideal Ic patut mempunyai datar dalan kawasan operasi kerana kecerunan minority tidak terjejas. Sebab kedua ialah voltan tepu tatarajah pemungut di bawah 0.1 V.

## LIST OF CONTENTS

|      |                                            | Pages                     |

|------|--------------------------------------------|---------------------------|

| DEC  | LARATION                                   | ii                        |

|      | TIFIED BY                                  | iii                       |

|      | NOWLEDGEMENT                               | iv                        |

|      | TRACT                                      | v                         |

| ABS  | TRAK                                       | vi                        |

| LIST | OF CONTENT                                 | vii                       |

| LIST | OF TABLES                                  | х                         |

| LIST | OF FIGURES                                 | xi                        |

| LIST | OF SYMBOLS                                 | xii                       |

| CHA  | APTER 1 INTRODUCTION                       | 1                         |

| 1.1  | Introduction                               | 1                         |

|      | 1.1.1 Silicon Technology                   | 2                         |

|      | 1.1.2 Structure and Principle of Operation | 2                         |

| 1.2  | Purpose                                    | 3                         |

| 1.3  | Project Objectives                         | 3                         |

| 1.4  | Project Scope                              | 4                         |

| CHA  | APTER 2 LITERATURE REVIEW                  | 5                         |

| 2.1  | Introduction                               | 5                         |

|      | 2.1.1 NPN Transistor                       | 5                         |

| 2.2  | Extrinsic Semiconductor                    | 6                         |

|      | 2.2.1 n-Type and p-Type Silicon            | 7                         |

| 2.3  | BJT configurations                         | 7                         |

|      | 2.3.1 Common-Collector                     | 8                         |

|      | 2.3.2 Common Emitter                       | 8                         |

|      | 2.3.3 Common Base                          | 9                         |

| 2.4  | Operating modes of the BJT                 | 9                         |

|      |                                            | UNIVERSITI MALAYSIA SABAI |

|     | 2.4.1  | Active                                          | 10                        |

|-----|--------|-------------------------------------------------|---------------------------|

|     | 2.4.2  | Cut-off                                         | 10                        |

|     | 2.4.3  | Saturation                                      | 11                        |

|     | 2.4.4  | Reverse active                                  | 11                        |

| 2.5 | Transi | istor Characteristics                           | 11                        |

|     | 2.5.1  | Static characteristics                          | 12                        |

|     | 2.5.2  | Dynamic Characteristics                         | 12                        |

|     | 2.5.3  | Current-Voltage Characteristics of a p-n Diodes | 14                        |

| 2.6 | Analy  | tical Relations for the Current                 | 15                        |

|     | 2.6.1  | Emitter Current                                 | 16                        |

|     | 2.6.2  | Collector Current                               | 17                        |

|     | 2.6.3  | Base Current                                    | 18                        |

| 2.7 | Curren | nt Gain                                         | 19                        |

|     | 2.7.1  | Common-Base                                     | 20                        |

|     | 2.7.2  | Common Emitter                                  | 20                        |

|     | 2.7.3  | Emitter Efficiency                              | 21                        |

|     | 2.7.4  | Base Transport Factor                           | 21                        |

|     | 2.7.5  | Collector Efficiency                            | 21                        |

| СНА | PTER   | 3 METHODOLOGY                                   | 22                        |

| 3.1 | Softw  | are                                             | 22                        |

| 3.2 | Overv  | view PISCES-IIB                                 | 22                        |

|     | 3.2.1  | Card Format                                     | 23                        |

|     | 3.2.2  | Card Sequence                                   | 24                        |

|     | 3.2.3  | Structure of NPN BJT                            | 35                        |

|     | 3.2.4  | Device Simulation                               | 27                        |

|     | 3.2.5  | Postmini                                        | 27                        |

|     | 3.2.6  | Analysis                                        | 27                        |

|     | 3.2.7  | Flowchart                                       | 28                        |

| CHA | PTER   | 4 RESULT AND DISCUSSION                         | 29                        |

| 4.1 | Stand  | ard Parameters                                  | 29                        |

|     | 4.1.1  | Structure and Simulator Description             | 29                        |

|     |        |                                                 | UNIVERSITI MALAYSIA SABAH |

viii

|      | 4.1.2  | Result and Discussion          | 30 |

|------|--------|--------------------------------|----|

| 4.2  | Increa | se Base Current                | 30 |

|      | 4.2.1  | Simulation Result              | 31 |

|      | 4.2.2  | Conclusion                     | 35 |

| 4.3  | Increa | se Concentration               | 35 |

|      | 4.3.1  | Simulation Result              | 36 |

| 4.4  | Resize | e The BJT Device Simulation    | 38 |

|      | 4.4.1  | Simulation Result              | 39 |

| СНА  | PTER 5 | 5 CONCLUSION AND FUTURE SCOPES | 42 |

| 5.1  | Concl  | usion                          | 42 |

| 5.2  | Future | e Scopes                       | 43 |

| REFE | ERENCI | E                              | 45 |

| ADDE | NDIX   |                                | 47 |

## LIST OF TABLES

| Num | umber of Table                             |    |

|-----|--------------------------------------------|----|

| 2.1 | Operating modes of the BJT                 | 10 |

| 3.1 | Simulation input parameters for npn BJT's. | 26 |

| 4.1 | Simulation input parameters.               | 29 |

| 4.2 | Simulation with difference concentration.  | 34 |

| 4.3 | Simulation with difference device size.    | 38 |

## LIST OF FIGURES

| Num | ber of Figure                                                                                        | Pages |

|-----|------------------------------------------------------------------------------------------------------|-------|

| 1.1 | Categories of Silicon Technology.                                                                    | 2     |

| 1.2 | Schematic cross section of a modern npn bipolar transistor.                                          | 3     |

| 2.1 | Direction of conventional current flow in a biased npn transistor.                                   | 8     |

| 2.2 | Common-emitter output characteristics.                                                               | 13    |

| 2.3 | Depletion regions, energy band diagram and carrier distribution.                                     |       |

|     | (a) Forward bias. (b) Reverse bias.                                                                  | 15    |

| 2.4 | An npn transistor with forward-biased emitter.                                                       | 17    |

| 2.5 | Carrier motion in the normal operation of an npn transistor                                          | 19    |

| 3.1 | Structures of npn BJT's.                                                                             | 25    |

| 3.2 | A rectangular mesh in two-dimension simulation.                                                      | 26    |

| 3.3 | Flowchart of npn BJT's                                                                               | 28    |

| 4.1 | Structure of the 4H-SiC BJT.                                                                         | 29    |

| 4.2 | Common-emitter I-V characteristics of a 4H-SiC bipolar                                               |       |

|     | junction transistor with 3x20 µm2 emitter at low current density.                                    |       |

|     | The applied base current is 20 µA (bottom trace), 40, 60, 80, 100,                                   |       |

|     | 120 and 140 μA (top trace).                                                                          | 30    |

| 4.3 | I-V characteristic curves for the common-emitter BJT transistor.                                     |       |

|     | $I_b$ increase from 20 $\mu$ A to 24 $\mu$ A.                                                        | 32    |

| 4.4 | I-V characteristic curves for the common-emitter BJT transistor.                                     |       |

|     | $I_b$ increase from 40 $\mu$ A to 44 $\mu$ A.                                                        | 33    |

| 4.5 | I-V characteristic curves for the common-emitter BJT transistor.                                     |       |

|     | $I_b$ increase from 60 $\mu$ A to 64 $\mu$ A.                                                        | 34    |

| 4.6 | I-V characteristic curves for the common-emitter BJT transistor.                                     | 37    |

| 4.7 | I-V characteristic curves for the common-emitter BJT transistor.                                     | 38    |

| 4.8 | I-V characteristic curves for the common-emitter BJT transistor. Oxide                               |       |

|     | thickness = 0.2 $\mu$ m, x-dimension = 4.5 $\mu$ m and y-dimension = 2.0 $\mu$ m.                    | 40    |

| 4.9 | I-V characteristic curves for the Common-emitter BJT transistor. Oxide                               |       |

|     | thickness = $0.7 \mu\text{m}$ , x-dimension = $10.5 \mu\text{m}$ and y-dimension = $5.2 \mu\text{m}$ | 41    |

## LIST OF SYMBOLS

| $E_C$           | minimum conduction band energy                                                    |

|-----------------|-----------------------------------------------------------------------------------|

| E <sub>Fn</sub> | Fermi level on the n-side of a pn junction                                        |

| $E_{Fp}$        | Fermi level on the p-side of a pn junction                                        |

| Ei              | intrinsic Fermi level                                                             |

| $E_V$           | maximum valence band energy                                                       |

| е               | exponent                                                                          |

| hfe             | common emitter current gain                                                       |

| $I_B$           | base current                                                                      |

| $I_C$           | collector current                                                                 |

| I <sub>Cn</sub> | DC collector current due to holes                                                 |

| ICp             | DC collector current due to electrons                                             |

| $I_E$           | emitter current                                                                   |

| I <sub>En</sub> | DC emitter current due to holes                                                   |

| IEp             | DC emitter current due to electrons                                               |

| Irec            | recombine current                                                                 |

| k               | boltzmann constant                                                                |

| Ln              | diffusion length of electrons                                                     |

| $L_p$           | diffusion length of holes                                                         |

| n <sub>E</sub>  | doping concentration in the BJT emitter                                           |

| ni              | intrinsic carrier concentration                                                   |

| nno             | electron concentration in n-type semiconductor (majority carriers) in             |

|                 | equilibrium                                                                       |

| np              | electron concentration in p-type semiconductor (minority carriers)                |

| n <sub>po</sub> | electron concentration in p-type semiconductor (minority carriers) in equilibrium |

| $P_n$           | hole concentration in n-type semiconductor (minority carriers)                    |

| Pno             | hole concentration in n-type semiconductor (minority carriers) in equilibrium     |

| Ppo            | hole concentration in p-type semiconductor (majority carriers) in |

|----------------|-------------------------------------------------------------------|

|                | equilibrium                                                       |

| q              | magnitude of the electronic charge                                |

| Т              | temperature in unit Kelvin                                        |

| $V_A$          | early voltage                                                     |

| $V_{BB}$       | DC supply voltage to BJT                                          |

| $V_{bi}$       | "built-in" junction voltage                                       |

| $V_{CE}$       | common emitter current                                            |

| $V_{CE(sat)}$  | saturation collector emitter current                              |

| Vceo           | collector-to-emitter breakdown voltage when $I_E=0$               |

| $V_{EB}$       | emitter base current                                              |

| $V_F$          | forward bias of rectifier                                         |

| $V_R$          | reverse bias of rectifier                                         |

| W              | device width                                                      |

| $W_B$          | total width of the base in a BJT                                  |

| X <sub>n</sub> | n-side width of the pn junction depletion region                  |

| $X_p$          | p-side width of the pn junction depletion region                  |

| $\alpha_0$     | common base current gain                                          |

| $\alpha_{T}$   | base transport factor                                             |

| β              | emitter base current gain                                         |

| Y              | emitter efficiency                                                |

| Al             | Aluminium                                                         |

| BJT            | bipolar junction transistor                                       |

| CMOS           | complementary metal-oxide-semiconductor                           |

direct current

that is

silicon

gallium arsenide

current-voltage

Metal Oxide Semiconductor

technology computer aided design

DC

i.e.

I-V

MOS

TCAD

Si

GaAs

#### **CHAPTER 1**

#### INTRODUCTION

## 1.1 Introduction

A bipolar junction transistor (BJT) is a type of transistor. It is a three-terminal device constructed of doped semiconductor material and may be used in amplifying or switching applications. Since the action of both electrons and holes is important in this device, it is called a bipolar transistor (Shur, 1996; Streetman, 1995).

PISCES-IIB device simulator is used to study the characteristics os silicon (Si) base device base BJT device. A common-emitter output characteristics current-voltage (I-V) graph show that the relationship between the DC current through an electronic device and the DC voltage across its terminals.

This paper focuses on the simulation of electrical I-V characteristics of npn bipolar junction transistor (BJT). The different of base current,  $I_b$ , concentration and device size parameters will effect the electrical I-V characteristics of the BJT.

### 1.1.1 Silicon Technology

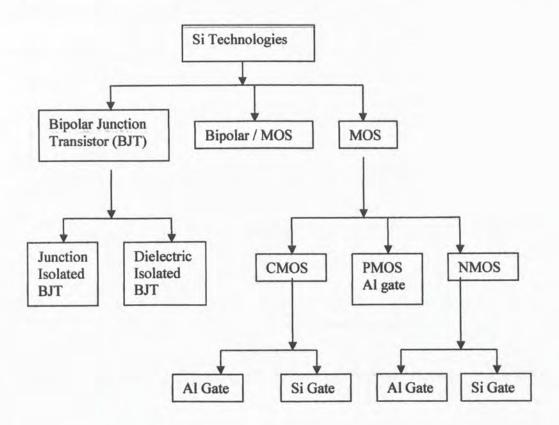

Figure 1.1 Categories of Silicon Technology

## 1.1.2 Structure and Principle of Operation

A bipolar junction transistor (BJT) is comprised of two back-to-back p-n junction (Kwyro *et al.*, 1993). This forms a sort of a sandwich where one kind of semiconductor is placed in between two others. There are two kinds of bipolar junction transistor, such as the *npn* and *pnp* varieties (Dorf, 2006). The three layers of the sandwich are conventionally called the collector, base, and emitter (Rutkowski & Oleksy, 1992).

The term bipolar means that the BJT's operation depends on the movement of two different carriers, such as electrons and holes. In *npn* BJT's, the electron is the majority carrier and the hole is the minority carrier.

#### 1.2 Purpose

To study the electrical current-voltage characteristics of the *npn* bipolar junction transistor (BJT) by using PISCES-IIB.

## 1.3 Project Objectives

- Design a bipolar junction transistor (BJT) device simulation by using PISCES-IIB.

- To study the electrical *I-V* characteristics of the BJT by increase the base current, I<sub>b</sub>.

• To study the electrical *I-V* characteristics of the BJT in different structure, such as width, depth and concentration parameters.

## 1.4 Project Scope

The scope of this research paper is analyzing the electrical current voltage characteristics of bipolar junction transistor by using PISCES-IIB. The parameter to be study are base current, depth, width, and concentration at room temperature, T=300K.

## **CHAPTER 2**

## LITERATURE REVIEW

## 2.1 Introduction

Semiconductor experiments at Bell Telephone Laboratories led to new theoretical concepts and William Shockley proposed an idea for a semiconductor amplifier that would critically test the theory (Smith, 1987). The actual device had far less amplification than predicted and John Bardeen suggested a revision of the theory. In December 1947, Bardeen and Walter Brattain discovered a new phenomenon and created a novel device (Smith, 1987). The next year Shockley invented the junction transistor. Nowadays, the use of the BJT has declined in favour of CMOS technology in the design of digital integrated circuits.

## 2.1.1 NPN Transistor

NPN is one of the two types of bipolar transistors, in which the letters "N" and "P" refer to the majority charge carriers inside the different regions of the transistor. Most

bipolar transistors used today are NPN, because electron mobility is higher than hole mobility in semiconductors, allowing greater currents and faster operation.

NPN transistors consist of a layer of P-doped semiconductor (the "base") between two N-doped layers. A small current entering the base in common-emitter mode is amplified in the collector output. In other terms, an NPN transistor is "on" when its base is pulled high relative to the emitter.

#### 2.2 Extrinsic Semiconductor

The impurity atoms frequently employed to dope pure silicon or germanium are the elements of group III and group V of the periodic table (Puri & Babbar, 1996). These group III or group V elements (materials) added to the pure semiconductor (mostly the silicon) are called impurities (Pokharel & Karki, 2007). The resulting semiconductor was known as extrinsic semiconductor (Pokharel & Karki, 2007). Obtain different type of extrinsic semiconductors by adding different types of impurities to the pure semiconductor. There are four valence electrons in silicon. By adding pentavalent impurities, such as arsenic, which had a valence of more than four will participate to form covalent bond with neighbouring silicon atoms (Kasap, 2006), whereas the fifth electron cannot participate in bonding since all the bonds are saturated. This extra electron to the conduction band of the semiconductor. Such semiconductors are called n-type. Similarly, we can obtained a p-type semiconductor by adding trivalent impurities like boron, aluminum, gallium, etc (Pokharel & Karki, 2007).

#### 2.2.1 n-Type and p-Type Silicon

Intrinsic silicon at room temperature had an extremely low free-carrier concentration. Therefore, its resistivity was very high (Yuan & Ning, 1998). Intrinsic silicon hardly exists at room temperature, since it would require materials with an unobtainable high purity. Most impurities in silicon introduce additional energy levels in the forbidden gap and can be easily ionized to add either electrons to the conduction band or holes to the valence band, depending on where the impurity level is (Yuan & Ning, 1998). The electrical conductivity of silicon was then dominated by the type and concentration of the impurity atoms, or dopants and the silicon was called extrinsic (Yuan & Ning, 1998).

## 2.3 BJT Configurations

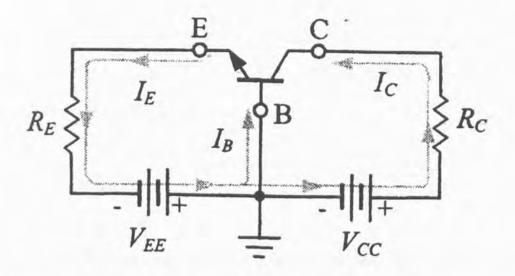

In a typical transistor circuit, the transistor was connected to an input circuit and an output circuit or load (Figure 2.1). (Additional components are often necessary to bias the BJT.) One of the terminals of the BJT (emitter, base or collector) was connected to both the input and the output circuit. The configuration of a BJT in a circuit was named after this common terminal. Thus, they are called common-emitter, common-base and common-collector configurations.

Figure 2.1 Direction of conventional current flow in a biased *npn* transistor (Aminian & Kazimierczuk, 2004).

## 2.3.1 Common-Collector

In an common-collector circuit with the collector connected to +V and a load connected between the emitter and ground, the voltage applied to the base minus the base emitter forward voltage drop (~0.6 V) will appear across the load (i.e., 5 V base = 4.4 V emitter). The only caveat was that the voltage source at the base must be able to supply about 5% of the load current without appreciable voltage drop. This was a non-inverting voltage follower circuit.

## 2.3.2 Common Emitter

In the common-collector, the emitter will be the common reference or the ground to both the base and the collector terminals (Aminian & Kazimierczuk, 2004) and +V, a voltage connected to the base which exceeds the base emitter forward voltage (0.6V)will rapidly turn on the transistor in proportion to the voltage rise as the base emitter

current rapidly increases for a small increase in base voltage. The base voltage source must be able to supply about 5% of the load current into the base emitter diode (i.e., short circuit) for the circuit to develop a large voltage across the load. This was an inverting voltage amplifier circuit.

#### 2.3.3 Common Base

The common-base stage was used primarily in high-frequency applications due to the fast that three was no direct capacitative feedback from output (collector) to input (emitter) as a result of the common or grounded base terminal (Whitaker, 2000). The base grounded (or at a reference voltage) and the load connected between the collector and +V, a control voltage connected to the emitter which was more negative than the base emitter forward voltage (~0.6V) causes the transistor to rapidly turn on. The control voltage source must be able to supply about 105% of the load current to develop the full voltage across the load. This was a non-inverting voltage amplifier circuit.

## 2.4 Operating modes of the BJT

The operating mode of a BJT depends on how its junctions are biased (Table 2.1). The active region of the BJT was defined by a forward-biased base-emitter junction and a reverse-biased collector base junction. This region was of importance in linear or amplifying application. Two other region of importance in switching application was the cutoff and saturation region (Comer, 2003). Most BJTs in digital circuits (logic

gates, memory) operate in these two modes. The reverse active mode was rarely used and was listed here for reference.

| Operating mode | Emitter-Base junction | Collector-Base junction |

|----------------|-----------------------|-------------------------|

| Active         | forward               | reverse                 |

| Cut-off        | reverse               | reverse                 |

| Saturation     | forward               | forward                 |

| Inverse        | reverse               | forward                 |

Table 2.1 Operating modes of the BJT (Ng, 2002).

## 2.4.1 Active

A transistor was said to be operating in the active region when the base-emitter junction was forward biased and the collector-base junction was reverse biased (Paynter, 2003). Most bipolar transistors are designed to afford the greatest commonemitter current gain,  $\beta_f$  in forward-active mode. If this was the case, the collectoremitter current was approximately proportional to the base current, but many times larger, for small base current variations.

## 2.4.2 Cut-off

When a transistor was in cutoff, both junction are reverse biased and the current through all three terminals was nearly zero (Paynter, 2003), which corresponds to a logical "off", or an open switch.

#### REFERENCE

- Aminian, Ali & Kazimierczuk, M. K. 2004. Electronic Devices: A Design Approach. Prentice Hall, Upper Saddle River, NJ.

- Comer, D. J. 2003. Fundamentals of Electronic Circuit Design. John Wiley & Sons, New York,

- Dorf, R. C. 2006. The Electrical Engineering Handbook. CRC/Taylor & Francis, Boca Raton.

- Kano, K. 1998. Semiconductor Devices. Prentice Hall, Upper Saddle River, New Jersey.

- Kasap, S. O. 2006. Principles of Electronic Materials and Devices. McGraw-Hill, Boston.

- Kwyro, L., Shur, M., Fjeldly, T. A. & Ytterdal, T. 1993. Semiconductor Device Modeling for VLSI: with the AIM-spice circuit simulator. Prentice-Hall, New Jersey.

- Mauro, Z. 1989. Semiconductor Devices. McGraw Hill, New York.

- Ng, K. K. 2002. Complete Guide to Semiconductor Devices. Wiley-Interscience, New York.

- Paynter, R. T. 2003. Introductory Electronic Devices and Circuits: Conventional Flow Version. Prentice Hall, Upper Saddle River, N.J.

- Perez-Wurfl, R. Krutsinger, J.T. Torvik, B. Van Zeghbroeck. 2001. 4H-SiC bipolar junction transistor with high current and power density. *Solid-State Electronics* 47, pp. 229-231.

- Pierret, R. F. 1996. Semiconductor Device Fundamentals. Addison-Wesley, Massachusetts.

- Pokharel, B. P. & Karki, N. R. 2007. Electrical Engineering Materials. Alpha Science International Ltd, Oxford, UK.

- Puri, R. K. & Babbar, V. K. 1996. Solid State Physics and Electronics. S. Chand & Company Ltd, New Delhi.

- Ritchie, G. J. 1993. Transistor Circuit Techniques: Discrete and Integrated. Chapman & Hall, London,

Rutkowski, G. B. & Oleksy, J. E. 1992. Solid-state Electronics. Glence, New York.

Shur, M. 1996. Introduction to Electronic Devices. John Wiley, New York.

Singh, J. 1994. Semiconductor Devices: An Introduction. McGraw-Hill, New York.

Smith, R. J. 1987. Electrinics: Circuit and Devices. John Wiley, New York.

Stanford University, 2004. Stanford of University TCAD Tools. http://www-tcad.stanford.edu/tcad/programs/oldftpable.html

- Streetman, B. G. 1995. Solid State Electronic Devices. Prentice Hall, Englewood Cliffs, New Jersey.

- Sze, S. M. 1985. Semiconductor Devices: Physics and Technology. John Wiley, New York.

- Whitaker, J. C. 2000. Semiconductor Devices and Circuits. CRC Press, Boca Raton, Florida.

- Yuan, T. & Ning, T. H. 1998. Fundamentals of Modern VLSI Devices. Cambridge University Press, New York.